##Explanation and background

I have a custom board with a SAMA5D27 processor, 0.5G DDR, 800x480 TFT.

All is running OK (latest version of LittlevGL) and I am playing with the samples before cracking on with my own interface, but I’m having an issue “optimizing” the display driver.

If I use a basic memcpy from the active buffer to a third (cached) buffer it works fine, but takes 50ms to execute which is no use really.

So I’ve now set it up to use 2 full sized screen buffers and believe that one will be written to while the other is being displayed. So all I need to do is effecively pass the pointer of the active buffer to the underlying display routines every time flush is called - there’s a function in existence to display a “base buffer” from a cached area of memory and I should be able to simply pass a new buffer to this.

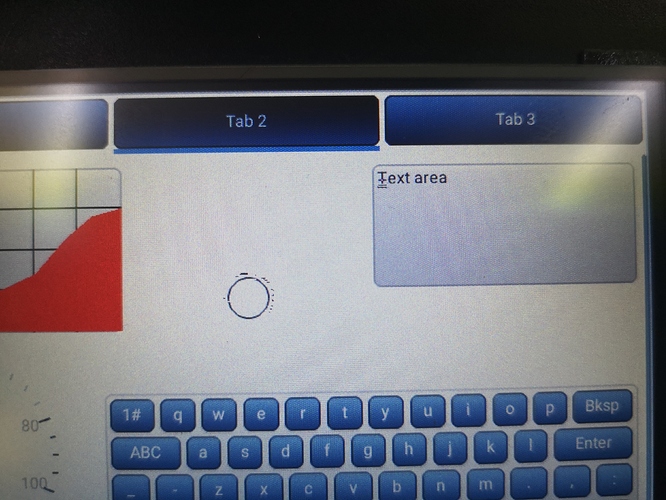

It works, only takes 10us to run, but I get horrible artefacts on areas of the screen that are being refreshed (e.g. the rotating circle of the lv_test_theme example on tab 2, and the blinking cursor on the same tab). It’s almost like the underlying update routines are actually writing to the buffer that’s being displaye.

If an action such as changing tabs is done on the screen, causing a whole screen scroll, and therefore the majority is being refreshed, it looks fine - so I know the buffers are being redrawn etc. And I’ve debugged it to ensure that “buf_act” is flipping each time flush is called.

Code to reproduce

CACHE_ALIGNED_DDR static lv_color_t lcd_buf_1[SIZE_LCD_BUFFER];

CACHE_ALIGNED_DDR static lv_color_t lcd_buf_2[SIZE_LCD_BUFFER];

cache_clean_region(lcd_buf_1, sizeof(lcd_buf_1));

cache_clean_region(lcd_buf_2, sizeof(lcd_buf_2));

static lv_disp_buf_t disp_buf;

lv_disp_buf_init(&disp_buf, lcd_buf_1, lcd_buf_2, SIZE_LCD_BUFFER);

lv_disp_drv_t disp_drv;

lv_disp_drv_init(&disp_drv);

disp_drv.buffer = &disp_buf;

disp_drv.flush_cb = lcd_disp_flush;

static void lcd_disp_flush(lv_disp_drv_t * disp_drv, const lv_area_t * area, lv_color_t * color_p)

{

lcdc_show_base(disp_drv->buffer->buf_act, 32, 0);

lv_disp_flush_ready(disp_drv);

}

Any suggestions of what I should be doing welcomed!

Screenshot and/or video

Here’s a screenshot - can’t think how to share a video at the moment!