Description

I created the software on cubemx to do all the processes myself in order. But the software I designed by creating my own configuration runs slower than the stm32f746 firmware portrayed for lvgl.

Portrayed software: https://github.com/lvgl/lv_port_stm32f746_disco

What MCU/Processor/Board and compiler are you using?

STM32F746G-Discovery

STM32CubeIDE

What LVGL version are you using?

7.7.2

What do you want to achieve?

What should I do to make the microcontroller work faster. What is this slowness caused by?

What have you tried so far?

I examined all of the software on the lv_port_stm32f746_disco and applied the procedures.

I am using SDRAM. Framebuffer is on SDRAM.

Color buffer is transferred to SDRAM by DMA.

I-Cache and D-Cache enabled.

LTDC, DMA, FMC settings are exactly the same. I copied it from lv_port_stm32f746_disco software.

LTDC clock freq is 9.6 MHz

Code to reproduce

/* USER CODE END Header */

/* Includes ------------------------------------------------------------------*/

#include "main.h"

/* Private includes ----------------------------------------------------------*/

/* USER CODE BEGIN Includes */

#include "lvgl/lvgl.h"

#include "lv_conf.h"

#include "lv_examples/lv_examples.h"

/* USER CODE END Includes */

/* Private variables ---------------------------------------------------------*/

LTDC_HandleTypeDef hltdc;

TIM_HandleTypeDef htim2;

DMA_HandleTypeDef hdma_memtomem_dma2_stream0;

SDRAM_HandleTypeDef hsdram1;

/* USER CODE BEGIN PV */

static FMC_SDRAM_CommandTypeDef Command;

/* USER CODE END PV */

/* Private function prototypes -----------------------------------------------*/

void SystemClock_Config(void);

static void MX_GPIO_Init(void);

static void MX_DMA_Init(void);

static void MX_FMC_Init(void);

static void MX_LTDC_Init(void);

static void MX_TIM2_Init(void);

/* USER CODE BEGIN PFP */

/* USER CODE END PFP */

/* Private user code ---------------------------------------------------------*/

/* USER CODE BEGIN 0 */

#define SDRAM_DEVICE_ADDR ((uint32_t)0xC0000000)

#define SDRAM_DEVICE_SIZE ((uint32_t)0x800000) /* SDRAM device size in MBytes */

/* #define SDRAM_MEMORY_WIDTH FMC_SDRAM_MEM_BUS_WIDTH_8 */

#define SDRAM_MEMORY_WIDTH FMC_SDRAM_MEM_BUS_WIDTH_16

#define SDCLOCK_PERIOD FMC_SDRAM_CLOCK_PERIOD_2

/* #define SDCLOCK_PERIOD FMC_SDRAM_CLOCK_PERIOD_3 */

#define REFRESH_COUNT ((uint32_t)0x0603) /* SDRAM refresh counter (100Mhz SD clock) */

#define SDRAM_TIMEOUT ((uint32_t)0xFFFF)

/* DMA definitions for SDRAM DMA transfer */

#define __DMAx_CLK_ENABLE __HAL_RCC_DMA2_CLK_ENABLE

#define __DMAx_CLK_DISABLE __HAL_RCC_DMA2_CLK_DISABLE

#define SDRAM_DMAx_CHANNEL DMA_CHANNEL_0

#define SDRAM_DMAx_STREAM DMA2_Stream0

#define SDRAM_DMAx_IRQn DMA2_Stream0_IRQn

#define BSP_SDRAM_DMA_IRQHandler DMA2_Stream0_IRQHandler

/**

* @}

*/

/**

* @brief FMC SDRAM Mode definition register defines

*/

#define SDRAM_MODEREG_BURST_LENGTH_1 ((uint16_t)0x0000)

#define SDRAM_MODEREG_BURST_LENGTH_2 ((uint16_t)0x0001)

#define SDRAM_MODEREG_BURST_LENGTH_4 ((uint16_t)0x0002)

#define SDRAM_MODEREG_BURST_LENGTH_8 ((uint16_t)0x0004)

#define SDRAM_MODEREG_BURST_TYPE_SEQUENTIAL ((uint16_t)0x0000)

#define SDRAM_MODEREG_BURST_TYPE_INTERLEAVED ((uint16_t)0x0008)

#define SDRAM_MODEREG_CAS_LATENCY_2 ((uint16_t)0x0020)

#define SDRAM_MODEREG_CAS_LATENCY_3 ((uint16_t)0x0030)

#define SDRAM_MODEREG_OPERATING_MODE_STANDARD ((uint16_t)0x0000)

#define SDRAM_MODEREG_WRITEBURST_MODE_PROGRAMMED ((uint16_t)0x0000)

#define SDRAM_MODEREG_WRITEBURST_MODE_SINGLE ((uint16_t)0x0200)

static __IO uint16_t * my_fb = (__IO uint16_t*) (SDRAM_DEVICE_ADDR);

typedef uint16_t uintpixel_t;

static lv_disp_t * disp;

static int32_t x1_flush;

static int32_t y1_flush;

static int32_t x2_flush;

static int32_t y2_fill;

static int32_t y_fill_act;

static lv_color_t * buf_to_flush;

static void tft_flush(lv_disp_drv_t * drv, const lv_area_t * area, lv_color_t * color_p);

void tft_init(void)

{

static lv_disp_buf_t disp_buf;

static lv_color_t buf_1[LV_HOR_RES_MAX * 68];

static lv_color_t buf_2[LV_HOR_RES_MAX * 68];

lv_disp_buf_init(&disp_buf, buf_1, buf_2, LV_HOR_RES_MAX * 68); /*Initialize the display buffer*/

/*-----------------------------------

* Register the display in LittlevGL

*----------------------------------*/

lv_disp_drv_t disp_drv; /*Descriptor of a display driver*/

lv_disp_drv_init(&disp_drv); /*Basic initialization*/

/*Set up the functions to access to your display*/

/*Set the resolution of the display*/

disp_drv.hor_res = 480;

disp_drv.ver_res = 272;

/*Used to copy the buffer's content to the display*/

disp_drv.flush_cb = tft_flush;

/*Set a display buffer*/

disp_drv.buffer = &disp_buf;

/*Finally register the driver*/

disp = lv_disp_drv_register(&disp_drv);

}

static void tft_flush(lv_disp_drv_t * drv, const lv_area_t * area, lv_color_t * color_p)

{

int32_t x1 = area->x1;

int32_t x2 = area->x2;

int32_t y1 = area->y1;

int32_t y2 = area->y2;

/*Return if the area is out the screen*/

if(x2 < 0) return;

if(y2 < 0) return;

if(x1 > 480 - 1) return;

if(y1 > 272 - 1) return;

/*Truncate the area to the screen*/

int32_t act_x1 = x1 < 0 ? 0 : x1;

int32_t act_y1 = y1 < 0 ? 0 : y1;

int32_t act_x2 = x2 > 480 - 1 ? 480 - 1 : x2;

int32_t act_y2 = y2 > 272 - 1 ? 272 - 1 : y2;

x1_flush = act_x1;

y1_flush = act_y1;

x2_flush = act_x2;

y2_fill = act_y2;

y_fill_act = act_y1;

buf_to_flush = color_p;

uint32_t length = (x2_flush - x1_flush + 1);

SCB_CleanInvalidateDCache();

SCB_InvalidateICache();

HAL_StatusTypeDef err;

err = HAL_DMA_Start_IT(&hdma_memtomem_dma2_stream0,(uint32_t)buf_to_flush, (uint32_t)&my_fb[y_fill_act * 480 + x1_flush],

length);

if(err != HAL_OK)

{

while(1);

}

}

static void DMA_TransferComplete(DMA_HandleTypeDef *han)

{

y_fill_act ++;

if(y_fill_act > y2_fill) {

SCB_CleanInvalidateDCache();

SCB_InvalidateICache();

lv_disp_flush_ready(&disp->driver);

} else {

uint32_t length = (x2_flush - x1_flush + 1);

buf_to_flush += x2_flush - x1_flush + 1;

/*##-7- Start the DMA transfer using the interrupt mode ####################*/

/* Configure the source, destination and buffer size DMA fields and Start DMA Stream transfer */

/* Enable All the DMA interrupts */

if(HAL_DMA_Start_IT(han,(uint32_t)buf_to_flush, (uint32_t)&my_fb[y_fill_act * 480 + x1_flush], length) != HAL_OK)

{

while(1); /*Halt on error*/

}

}

}

static void DMA_TransferError(DMA_HandleTypeDef *han)

{

}

/* USER CODE END 0 */

/**

* @brief The application entry point.

* @retval int

*/

int main(void)

{

/* USER CODE BEGIN 1 */

/* USER CODE END 1 */

/* Enable I-Cache---------------------------------------------------------*/

SCB_EnableICache();

/* Enable D-Cache---------------------------------------------------------*/

SCB_EnableDCache();

/* MCU Configuration--------------------------------------------------------*/

/* Reset of all peripherals, Initializes the Flash interface and the Systick. */

HAL_Init();

/* USER CODE BEGIN Init */

/* USER CODE END Init */

/* Configure the system clock */

SystemClock_Config();

/* USER CODE BEGIN SysInit */

/* USER CODE END SysInit */

/* Initialize all configured peripherals */

MX_GPIO_Init();

MX_DMA_Init();

MX_FMC_Init();

MX_LTDC_Init();

MX_TIM2_Init();

/* USER CODE BEGIN 2 */

lv_init();

tft_init();

lv_demo_stress();

HAL_TIM_Base_Start_IT(&htim2);

/* USER CODE END 2 */

/* Infinite loop */

/* USER CODE BEGIN WHILE */

while (1)

{

/* USER CODE END WHILE */

/* USER CODE BEGIN 3 */

lv_task_handler();

HAL_Delay(10);

}

/* USER CODE END 3 */

}

/**

* @brief System Clock Configuration

* @retval None

*/

void SystemClock_Config(void)

{

RCC_OscInitTypeDef RCC_OscInitStruct = {0};

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};

RCC_PeriphCLKInitTypeDef PeriphClkInitStruct = {0};

/** Configure LSE Drive Capability

*/

HAL_PWR_EnableBkUpAccess();

/** Configure the main internal regulator output voltage

*/

__HAL_RCC_PWR_CLK_ENABLE();

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE1);

/** Initializes the RCC Oscillators according to the specified parameters

* in the RCC_OscInitTypeDef structure.

*/

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.HSEState = RCC_HSE_ON;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

RCC_OscInitStruct.PLL.PLLM = 25;

RCC_OscInitStruct.PLL.PLLN = 400;

RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV2;

RCC_OscInitStruct.PLL.PLLQ = 9;

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

{

Error_Handler();

}

/** Activate the Over-Drive mode

*/

if (HAL_PWREx_EnableOverDrive() != HAL_OK)

{

Error_Handler();

}

/** Initializes the CPU, AHB and APB buses clocks

*/

RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_HCLK|RCC_CLOCKTYPE_SYSCLK

|RCC_CLOCKTYPE_PCLK1|RCC_CLOCKTYPE_PCLK2;

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1;

RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV4;

RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV2;

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_6) != HAL_OK)

{

Error_Handler();

}

PeriphClkInitStruct.PeriphClockSelection = RCC_PERIPHCLK_LTDC;

PeriphClkInitStruct.PLLSAI.PLLSAIN = 384;

PeriphClkInitStruct.PLLSAI.PLLSAIR = 5;

PeriphClkInitStruct.PLLSAI.PLLSAIQ = 2;

PeriphClkInitStruct.PLLSAI.PLLSAIP = RCC_PLLSAIP_DIV8;

PeriphClkInitStruct.PLLSAIDivQ = 1;

PeriphClkInitStruct.PLLSAIDivR = RCC_PLLSAIDIVR_8;

if (HAL_RCCEx_PeriphCLKConfig(&PeriphClkInitStruct) != HAL_OK)

{

Error_Handler();

}

}

/**

* @brief LTDC Initialization Function

* @param None

* @retval None

*/

static void MX_LTDC_Init(void)

{

/* USER CODE BEGIN LTDC_Init 0 */

/* USER CODE END LTDC_Init 0 */

LTDC_LayerCfgTypeDef pLayerCfg = {0};

/* USER CODE BEGIN LTDC_Init 1 */

/* USER CODE END LTDC_Init 1 */

hltdc.Instance = LTDC;

hltdc.Init.HSPolarity = LTDC_HSPOLARITY_AL;

hltdc.Init.VSPolarity = LTDC_VSPOLARITY_AL;

hltdc.Init.DEPolarity = LTDC_DEPOLARITY_AL;

hltdc.Init.PCPolarity = LTDC_PCPOLARITY_IPC;

hltdc.Init.HorizontalSync = 40;

hltdc.Init.VerticalSync = 9;

hltdc.Init.AccumulatedHBP = 53;

hltdc.Init.AccumulatedVBP = 11;

hltdc.Init.AccumulatedActiveW = 533;

hltdc.Init.AccumulatedActiveH = 283;

hltdc.Init.TotalWidth = 565;

hltdc.Init.TotalHeigh = 285;

hltdc.Init.Backcolor.Blue = 0;

hltdc.Init.Backcolor.Green = 0;

hltdc.Init.Backcolor.Red = 0;

if (HAL_LTDC_Init(&hltdc) != HAL_OK)

{

Error_Handler();

}

pLayerCfg.WindowX0 = 0;

pLayerCfg.WindowX1 = 480;

pLayerCfg.WindowY0 = 0;

pLayerCfg.WindowY1 = 272;

pLayerCfg.PixelFormat = LTDC_PIXEL_FORMAT_RGB565;

pLayerCfg.Alpha = 255;

pLayerCfg.Alpha0 = 0;

pLayerCfg.BlendingFactor1 = LTDC_BLENDING_FACTOR1_PAxCA;

pLayerCfg.BlendingFactor2 = LTDC_BLENDING_FACTOR2_PAxCA;

pLayerCfg.FBStartAdress = (uint32_t)my_fb;

pLayerCfg.ImageWidth = 480;

pLayerCfg.ImageHeight = 272;

pLayerCfg.Backcolor.Blue = 0;

pLayerCfg.Backcolor.Green = 0;

pLayerCfg.Backcolor.Red = 0;

if (HAL_LTDC_ConfigLayer(&hltdc, &pLayerCfg, 0) != HAL_OK)

{

Error_Handler();

}

/* USER CODE BEGIN LTDC_Init 2 */

/* USER CODE END LTDC_Init 2 */

}

/**

* @brief TIM2 Initialization Function

* @param None

* @retval None

*/

static void MX_TIM2_Init(void)

{

/* USER CODE BEGIN TIM2_Init 0 */

/* USER CODE END TIM2_Init 0 */

TIM_ClockConfigTypeDef sClockSourceConfig = {0};

TIM_MasterConfigTypeDef sMasterConfig = {0};

/* USER CODE BEGIN TIM2_Init 1 */

/* USER CODE END TIM2_Init 1 */

htim2.Instance = TIM2;

htim2.Init.Prescaler = 10000;

htim2.Init.CounterMode = TIM_COUNTERMODE_UP;

htim2.Init.Period = 10;

htim2.Init.ClockDivision = TIM_CLOCKDIVISION_DIV1;

htim2.Init.AutoReloadPreload = TIM_AUTORELOAD_PRELOAD_DISABLE;

if (HAL_TIM_Base_Init(&htim2) != HAL_OK)

{

Error_Handler();

}

sClockSourceConfig.ClockSource = TIM_CLOCKSOURCE_INTERNAL;

if (HAL_TIM_ConfigClockSource(&htim2, &sClockSourceConfig) != HAL_OK)

{

Error_Handler();

}

sMasterConfig.MasterOutputTrigger = TIM_TRGO_RESET;

sMasterConfig.MasterSlaveMode = TIM_MASTERSLAVEMODE_DISABLE;

if (HAL_TIMEx_MasterConfigSynchronization(&htim2, &sMasterConfig) != HAL_OK)

{

Error_Handler();

}

/* USER CODE BEGIN TIM2_Init 2 */

/* USER CODE END TIM2_Init 2 */

}

/**

* Enable DMA controller clock

* Configure DMA for memory to memory transfers

* hdma_memtomem_dma2_stream0

*/

static void MX_DMA_Init(void)

{

/* DMA controller clock enable */

__HAL_RCC_DMA2_CLK_ENABLE();

/* Configure DMA request hdma_memtomem_dma2_stream0 on DMA2_Stream0 */

hdma_memtomem_dma2_stream0.Instance = DMA2_Stream0;

hdma_memtomem_dma2_stream0.Init.Channel = DMA_CHANNEL_0;

hdma_memtomem_dma2_stream0.Init.Direction = DMA_MEMORY_TO_MEMORY;

hdma_memtomem_dma2_stream0.Init.PeriphInc = DMA_PINC_ENABLE;

hdma_memtomem_dma2_stream0.Init.MemInc = DMA_MINC_ENABLE;

hdma_memtomem_dma2_stream0.Init.PeriphDataAlignment = DMA_PDATAALIGN_HALFWORD;

hdma_memtomem_dma2_stream0.Init.MemDataAlignment = DMA_MDATAALIGN_HALFWORD;

hdma_memtomem_dma2_stream0.Init.Mode = DMA_NORMAL;

hdma_memtomem_dma2_stream0.Init.Priority = DMA_PRIORITY_HIGH;

hdma_memtomem_dma2_stream0.Init.FIFOMode = DMA_FIFOMODE_ENABLE;

hdma_memtomem_dma2_stream0.Init.FIFOThreshold = DMA_FIFO_THRESHOLD_1QUARTERFULL;

hdma_memtomem_dma2_stream0.Init.MemBurst = DMA_MBURST_SINGLE;

hdma_memtomem_dma2_stream0.Init.PeriphBurst = DMA_PBURST_SINGLE;

if (HAL_DMA_Init(&hdma_memtomem_dma2_stream0) != HAL_OK)

{

Error_Handler( );

}

/* DMA interrupt init */

HAL_DMA_RegisterCallback(&hdma_memtomem_dma2_stream0, HAL_DMA_XFER_CPLT_CB_ID, DMA_TransferComplete);

HAL_DMA_RegisterCallback(&hdma_memtomem_dma2_stream0, HAL_DMA_XFER_ERROR_CB_ID, DMA_TransferError);

/* DMA2_Stream0_IRQn interrupt configuration */

HAL_NVIC_SetPriority(DMA2_Stream0_IRQn, 0, 0);

HAL_NVIC_EnableIRQ(DMA2_Stream0_IRQn);

}

/* FMC initialization function */

static void MX_FMC_Init(void)

{

/* USER CODE BEGIN FMC_Init 0 */

/* USER CODE END FMC_Init 0 */

FMC_SDRAM_TimingTypeDef SdramTiming = {0};

/* USER CODE BEGIN FMC_Init 1 */

/* USER CODE END FMC_Init 1 */

/** Perform the SDRAM1 memory initialization sequence

*/

hsdram1.Instance = FMC_SDRAM_DEVICE;

/* hsdram1.Init */

hsdram1.Init.SDBank = FMC_SDRAM_BANK1;

hsdram1.Init.ColumnBitsNumber = FMC_SDRAM_COLUMN_BITS_NUM_8;

hsdram1.Init.RowBitsNumber = FMC_SDRAM_ROW_BITS_NUM_12;

hsdram1.Init.MemoryDataWidth = FMC_SDRAM_MEM_BUS_WIDTH_16;

hsdram1.Init.InternalBankNumber = FMC_SDRAM_INTERN_BANKS_NUM_4;

hsdram1.Init.CASLatency = FMC_SDRAM_CAS_LATENCY_2;

hsdram1.Init.WriteProtection = FMC_SDRAM_WRITE_PROTECTION_DISABLE;

hsdram1.Init.SDClockPeriod = FMC_SDRAM_CLOCK_PERIOD_2;

hsdram1.Init.ReadBurst = FMC_SDRAM_RBURST_ENABLE;

hsdram1.Init.ReadPipeDelay = FMC_SDRAM_RPIPE_DELAY_0;

/* SdramTiming */

SdramTiming.LoadToActiveDelay = 2;

SdramTiming.ExitSelfRefreshDelay = 7;

SdramTiming.SelfRefreshTime = 4;

SdramTiming.RowCycleDelay = 7;

SdramTiming.WriteRecoveryTime = 2;

SdramTiming.RPDelay = 2;

SdramTiming.RCDDelay = 2;

if (HAL_SDRAM_Init(&hsdram1, &SdramTiming) != HAL_OK)

{

Error_Handler( );

}

/* USER CODE BEGIN FMC_Init 2 */

__IO uint32_t tmpmrd = 0;

/* Step 1: Configure a clock configuration enable command */

Command.CommandMode = FMC_SDRAM_CMD_CLK_ENABLE;

Command.CommandTarget = FMC_SDRAM_CMD_TARGET_BANK1;

Command.AutoRefreshNumber = 1;

Command.ModeRegisterDefinition = 0;

/* Send the command */

HAL_SDRAM_SendCommand(&hsdram1, &Command, SDRAM_TIMEOUT);

/* Step 2: Insert 100 us minimum delay */

/* Inserted delay is equal to 1 ms due to systick time base unit (ms) */

HAL_Delay(1);

/* Step 3: Configure a PALL (precharge all) command */

Command.CommandMode = FMC_SDRAM_CMD_PALL;

Command.CommandTarget = FMC_SDRAM_CMD_TARGET_BANK1;

Command.AutoRefreshNumber = 1;

Command.ModeRegisterDefinition = 0;

/* Send the command */

HAL_SDRAM_SendCommand(&hsdram1, &Command, SDRAM_TIMEOUT);

/* Step 4: Configure an Auto Refresh command */

Command.CommandMode = FMC_SDRAM_CMD_AUTOREFRESH_MODE;

Command.CommandTarget = FMC_SDRAM_CMD_TARGET_BANK1;

Command.AutoRefreshNumber = 8;

Command.ModeRegisterDefinition = 0;

/* Send the command */

HAL_SDRAM_SendCommand(&hsdram1, &Command, SDRAM_TIMEOUT);

/* Step 5: Program the external memory mode register */

tmpmrd = (uint32_t)SDRAM_MODEREG_BURST_LENGTH_1 |\

SDRAM_MODEREG_BURST_TYPE_SEQUENTIAL |\

SDRAM_MODEREG_CAS_LATENCY_2 |\

SDRAM_MODEREG_OPERATING_MODE_STANDARD |\

SDRAM_MODEREG_WRITEBURST_MODE_SINGLE;

Command.CommandMode = FMC_SDRAM_CMD_LOAD_MODE;

Command.CommandTarget = FMC_SDRAM_CMD_TARGET_BANK1;

Command.AutoRefreshNumber = 1;

Command.ModeRegisterDefinition = tmpmrd;

/* Send the command */

HAL_SDRAM_SendCommand(&hsdram1, &Command, SDRAM_TIMEOUT);

/* Step 6: Set the refresh rate counter */

/* Set the device refresh rate */

HAL_SDRAM_ProgramRefreshRate(&hsdram1, REFRESH_COUNT);

/* USER CODE END FMC_Init 2 */

}

/**

* @brief GPIO Initialization Function

* @param None

* @retval None

*/

static void MX_GPIO_Init(void)

{

// ....GPIO init......

}

/* USER CODE BEGIN 4 */

/* USER CODE END 4 */

/**

* @brief Period elapsed callback in non blocking mode

* @note This function is called when TIM6 interrupt took place, inside

* HAL_TIM_IRQHandler(). It makes a direct call to HAL_IncTick() to increment

* a global variable "uwTick" used as application time base.

* @param htim : TIM handle

* @retval None

*/

void HAL_TIM_PeriodElapsedCallback(TIM_HandleTypeDef *htim)

{

/* USER CODE BEGIN Callback 0 */

/* USER CODE END Callback 0 */

if (htim->Instance == TIM6) {

HAL_IncTick();

}

else if (htim->Instance == TIM2) {

lv_tick_inc(1);

HAL_GPIO_TogglePin(LED_GPIO_Port, LED_Pin);

}

/* USER CODE BEGIN Callback 1 */

/* USER CODE END Callback 1 */

}

/**

* @brief This function is executed in case of error occurrence.

* @retval None

*/

void Error_Handler(void)

{

/* USER CODE BEGIN Error_Handler_Debug */

/* User can add his own implementation to report the HAL error return state */

__disable_irq();

while (1)

{

}

/* USER CODE END Error_Handler_Debug */

}

#ifdef USE_FULL_ASSERT

/**

* @brief Reports the name of the source file and the source line number

* where the assert_param error has occurred.

* @param file: pointer to the source file name

* @param line: assert_param error line source number

* @retval None

*/

void assert_failed(uint8_t *file, uint32_t line)

{

/* USER CODE BEGIN 6 */

/* User can add his own implementation to report the file name and line number,

ex: printf("Wrong parameters value: file %s on line %d\r\n", file, line) */

/* USER CODE END 6 */

}

#endif /* USE_FULL_ASSERT */

/************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

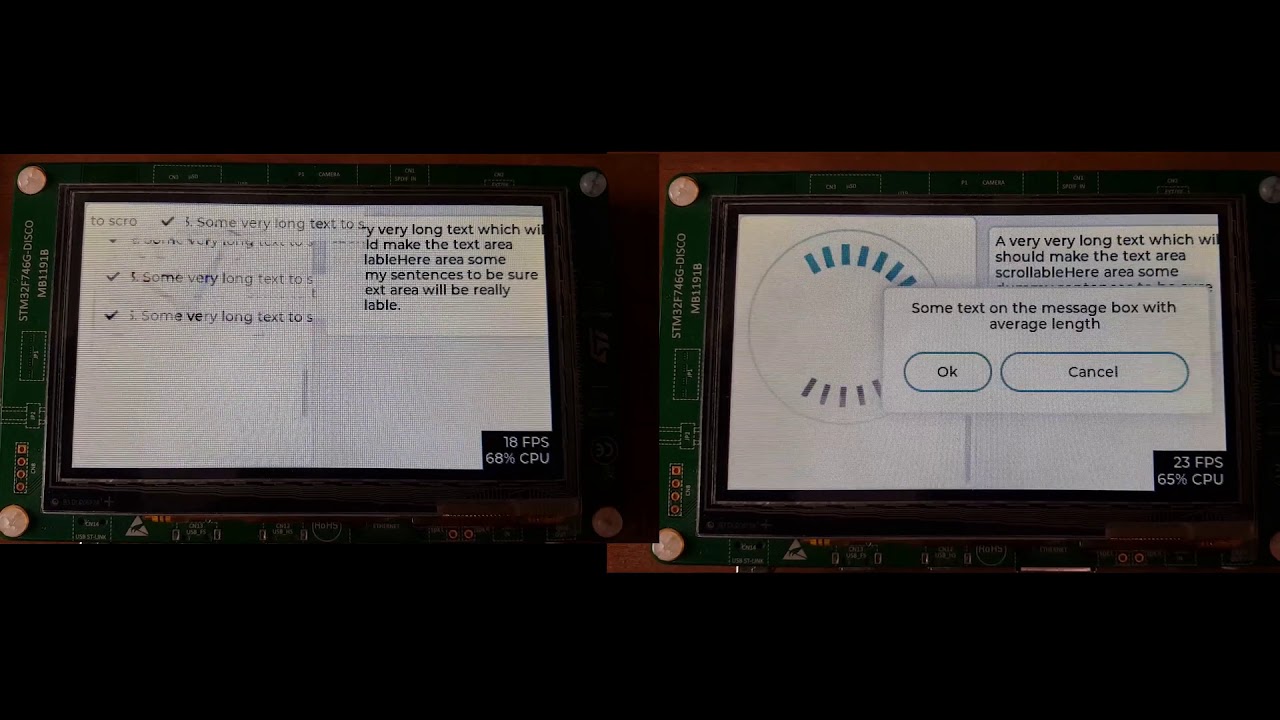

Screenshot and/or video

Left one is my software, right one is lv_port_stm32f746_disco software