Description

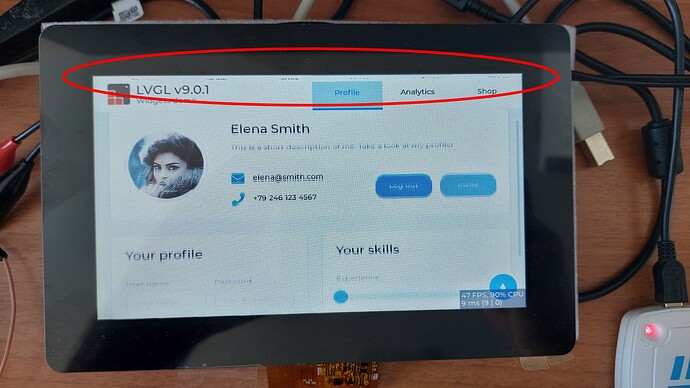

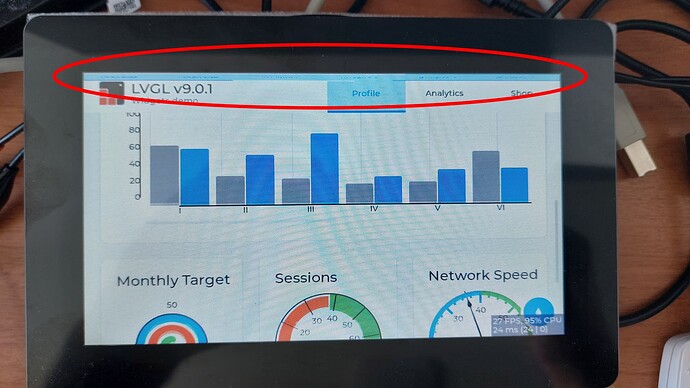

Hello, I am trying to drive 7" (800x480) TFT-LCD with stm32h743 controller. It works fine when I use DMA. But when I use it with DMA2D, there is distortion in the first few lines. DMA2D seems to start from the wrong offset. How can I solve this problem?

What MCU/Processor/Board and compiler are you using?

Open746I-C - Waveshare Development Board

STM32H743IITX

STM32CubeIDE v1.14.0

What LVGL version are you using?

9.0.1

What do you want to achieve?

Driving the screen using DMA2D

What have you tried so far?

I was able to drive the screen with DMA without any problems.

Code to reproduce

TFT Flush section

static void tft_flush_cb(lv_disp_t * disp, const lv_area_t * area, uint8_t * pxmap)

{

SCB_CleanInvalidateDCache();

SCB_InvalidateICache();

/*Truncate the area to the screen*/

int32_t act_x1 = area->x1 < 0 ? 0 : area->x1;

int32_t act_y1 = area->y1 < 0 ? 0 : area->y1;

x1_flush = act_x1;

y1_flush = act_y1;

lv_coord_t width = lv_area_get_width(area);

lv_coord_t height = lv_area_get_height(area);

if (HAL_DMA2D_Start(&hdma2d, pxmap, (uint32_t)&my_fb[act_y1 * TFT_HOR_RES + act_x1], width, height) == HAL_OK)

{

/* Polling For DMA transfer */

HAL_DMA2D_PollForTransfer(&hdma2d, 1);

lv_disp_flush_ready(disp);

}

}

All code

/* USER CODE BEGIN Header */

/**

******************************************************************************

* @file : main.c

* @brief : Main program body

******************************************************************************

* @attention

*

* Copyright (c) 2024 STMicroelectronics.

* All rights reserved.

*

* This software is licensed under terms that can be found in the LICENSE file

* in the root directory of this software component.

* If no LICENSE file comes with this software, it is provided AS-IS.

*

******************************************************************************

*/

/* USER CODE END Header */

/* Includes ------------------------------------------------------------------*/

#include "main.h"

/* Private includes ----------------------------------------------------------*/

/* USER CODE BEGIN Includes */

#include "lvgl.h"

#include "demos/lv_demos.h"

/* USER CODE END Includes */

/* Private typedef -----------------------------------------------------------*/

/* USER CODE BEGIN PTD */

/* USER CODE END PTD */

/* Private define ------------------------------------------------------------*/

/* USER CODE BEGIN PD */

#define TFT_HOR_RES 800

#define TFT_VER_RES 480

/* USER CODE END PD */

/* Private macro -------------------------------------------------------------*/

/* USER CODE BEGIN PM */

/* USER CODE END PM */

/* Private variables ---------------------------------------------------------*/

DMA2D_HandleTypeDef hdma2d;

LTDC_HandleTypeDef hltdc;

TIM_HandleTypeDef htim2;

SDRAM_HandleTypeDef hsdram1;

/* USER CODE BEGIN PV */

static FMC_SDRAM_CommandTypeDef Command;

static lv_display_t * disp;

/* USER CODE END PV */

/* Private function prototypes -----------------------------------------------*/

void SystemClock_Config(void);

static void MPU_Config(void);

static void MX_GPIO_Init(void);

static void MX_LTDC_Init(void);

static void MX_FMC_Init(void);

static void MX_TIM2_Init(void);

static void MX_DMA2D_Init(void);

/* USER CODE BEGIN PFP */

/* USER CODE END PFP */

/* Private user code ---------------------------------------------------------*/

/* USER CODE BEGIN 0 */

#define SDRAM_DEVICE_ADDR ((uint32_t)0xD0000000)

#define SDRAM_DEVICE_SIZE ((uint32_t)0x800000) /* SDRAM device size in MBytes */

/* #define SDRAM_MEMORY_WIDTH FMC_SDRAM_MEM_BUS_WIDTH_8 */

#define SDRAM_MEMORY_WIDTH FMC_SDRAM_MEM_BUS_WIDTH_16

#define SDCLOCK_PERIOD FMC_SDRAM_CLOCK_PERIOD_2

/* #define SDCLOCK_PERIOD FMC_SDRAM_CLOCK_PERIOD_3 */

#define REFRESH_COUNT ((uint32_t)0x0603) /* SDRAM refresh counter (100Mhz SD clock) */

#define SDRAM_TIMEOUT ((uint32_t)0xFFFF)

/* DMA definitions for SDRAM DMA transfer */

#define __DMAx_CLK_ENABLE __HAL_RCC_DMA2_CLK_ENABLE

#define __DMAx_CLK_DISABLE __HAL_RCC_DMA2_CLK_DISABLE

#define SDRAM_DMAx_CHANNEL DMA_CHANNEL_0

#define SDRAM_DMAx_STREAM DMA2_Stream0

#define SDRAM_DMAx_IRQn DMA2_Stream0_IRQn

#define BSP_SDRAM_DMA_IRQHandler DMA2_Stream0_IRQHandler

/**

* @}

*/

/**

* @brief FMC SDRAM Mode definition register defines

*/

#define SDRAM_MODEREG_BURST_LENGTH_1 ((uint16_t)0x0000)

#define SDRAM_MODEREG_BURST_LENGTH_2 ((uint16_t)0x0001)

#define SDRAM_MODEREG_BURST_LENGTH_4 ((uint16_t)0x0002)

#define SDRAM_MODEREG_BURST_LENGTH_8 ((uint16_t)0x0004)

#define SDRAM_MODEREG_BURST_TYPE_SEQUENTIAL ((uint16_t)0x0000)

#define SDRAM_MODEREG_BURST_TYPE_INTERLEAVED ((uint16_t)0x0008)

#define SDRAM_MODEREG_CAS_LATENCY_2 ((uint16_t)0x0020)

#define SDRAM_MODEREG_CAS_LATENCY_3 ((uint16_t)0x0030)

#define SDRAM_MODEREG_OPERATING_MODE_STANDARD ((uint16_t)0x0000)

#define SDRAM_MODEREG_WRITEBURST_MODE_PROGRAMMED ((uint16_t)0x0000)

#define SDRAM_MODEREG_WRITEBURST_MODE_SINGLE ((uint16_t)0x0200)

static __IO uint16_t * my_fb = (__IO uint16_t*) (SDRAM_DEVICE_ADDR);

static __attribute__((aligned(32))) lv_color_t buf_1[TFT_HOR_RES * 94];

static __attribute__((aligned(32))) lv_color_t buf_2[TFT_HOR_RES * 94];

static volatile int32_t x1_flush;

static volatile int32_t y1_flush;

static void tft_flush_cb(lv_disp_t * disp, const lv_area_t * area, uint8_t * pxmap)

{

SCB_CleanInvalidateDCache();

SCB_InvalidateICache();

/*Truncate the area to the screen*/

int32_t act_x1 = area->x1 < 0 ? 0 : area->x1;

int32_t act_y1 = area->y1 < 0 ? 0 : area->y1;

x1_flush = act_x1;

y1_flush = act_y1;

lv_coord_t width = lv_area_get_width(area);

lv_coord_t height = lv_area_get_height(area);

if (HAL_DMA2D_Start(&hdma2d, pxmap, (uint32_t)&my_fb[act_y1 * TFT_HOR_RES + act_x1], width, height) == HAL_OK)

{

/* Polling For DMA transfer */

HAL_DMA2D_PollForTransfer(&hdma2d, 1);

lv_disp_flush_ready(disp);

}

}

/* USER CODE END 0 */

/**

* @brief The application entry point.

* @retval int

*/

int main(void)

{

/* USER CODE BEGIN 1 */

/* USER CODE END 1 */

/* MPU Configuration--------------------------------------------------------*/

MPU_Config();

/* Enable the CPU Cache */

/* Enable I-Cache---------------------------------------------------------*/

SCB_EnableICache();

/* Enable D-Cache---------------------------------------------------------*/

SCB_EnableDCache();

/* MCU Configuration--------------------------------------------------------*/

/* Reset of all peripherals, Initializes the Flash interface and the Systick. */

HAL_Init();

/* USER CODE BEGIN Init */

/* USER CODE END Init */

/* Configure the system clock */

SystemClock_Config();

/* USER CODE BEGIN SysInit */

/* USER CODE END SysInit */

/* Initialize all configured peripherals */

MX_GPIO_Init();

MX_LTDC_Init();

MX_FMC_Init();

MX_TIM2_Init();

MX_DMA2D_Init();

/* USER CODE BEGIN 2 */

HAL_LTDC_SetAddress(&hltdc, (uint32_t)my_fb, 0);

lv_init();

disp = lv_display_create(TFT_HOR_RES, TFT_VER_RES); /*Basic initialization with horizontal and vertical resolution in pixels*/

lv_display_set_flush_cb(disp, tft_flush_cb); /*Set a flush callback to draw to the display*/

lv_display_set_buffers(disp, buf_1, buf_2, TFT_HOR_RES * 94, LV_DISPLAY_RENDER_MODE_PARTIAL); /*Set an initialized buffer*/

lv_demo_widgets();

lv_demo_widgets_start_slideshow();

//lv_demo_benchmark();

//lv_demo_stress();

/* USER CODE END 2 */

/* Infinite loop */

/* USER CODE BEGIN WHILE */

while (1)

{

/* USER CODE END WHILE */

/* USER CODE BEGIN 3 */

lv_timer_handler();

HAL_Delay(1);

}

/* USER CODE END 3 */

}

/**

* @brief System Clock Configuration

* @retval None

*/

void SystemClock_Config(void)

{

RCC_OscInitTypeDef RCC_OscInitStruct = {0};

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};

/** Supply configuration update enable

*/

HAL_PWREx_ConfigSupply(PWR_LDO_SUPPLY);

/** Configure the main internal regulator output voltage

*/

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE1);

while(!__HAL_PWR_GET_FLAG(PWR_FLAG_VOSRDY)) {}

__HAL_RCC_SYSCFG_CLK_ENABLE();

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE0);

while(!__HAL_PWR_GET_FLAG(PWR_FLAG_VOSRDY)) {}

/** Initializes the RCC Oscillators according to the specified parameters

* in the RCC_OscInitTypeDef structure.

*/

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSI;

RCC_OscInitStruct.HSIState = RCC_HSI_DIV1;

RCC_OscInitStruct.HSICalibrationValue = RCC_HSICALIBRATION_DEFAULT;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSI;

RCC_OscInitStruct.PLL.PLLM = 4;

RCC_OscInitStruct.PLL.PLLN = 60;

RCC_OscInitStruct.PLL.PLLP = 2;

RCC_OscInitStruct.PLL.PLLQ = 2;

RCC_OscInitStruct.PLL.PLLR = 2;

RCC_OscInitStruct.PLL.PLLRGE = RCC_PLL1VCIRANGE_3;

RCC_OscInitStruct.PLL.PLLVCOSEL = RCC_PLL1VCOWIDE;

RCC_OscInitStruct.PLL.PLLFRACN = 0;

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

{

Error_Handler();

}

/** Initializes the CPU, AHB and APB buses clocks

*/

RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_HCLK|RCC_CLOCKTYPE_SYSCLK

|RCC_CLOCKTYPE_PCLK1|RCC_CLOCKTYPE_PCLK2

|RCC_CLOCKTYPE_D3PCLK1|RCC_CLOCKTYPE_D1PCLK1;

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

RCC_ClkInitStruct.SYSCLKDivider = RCC_SYSCLK_DIV1;

RCC_ClkInitStruct.AHBCLKDivider = RCC_HCLK_DIV2;

RCC_ClkInitStruct.APB3CLKDivider = RCC_APB3_DIV2;

RCC_ClkInitStruct.APB1CLKDivider = RCC_APB1_DIV2;

RCC_ClkInitStruct.APB2CLKDivider = RCC_APB2_DIV2;

RCC_ClkInitStruct.APB4CLKDivider = RCC_APB4_DIV2;

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_4) != HAL_OK)

{

Error_Handler();

}

}

/**

* @brief DMA2D Initialization Function

* @param None

* @retval None

*/

static void MX_DMA2D_Init(void)

{

/* USER CODE BEGIN DMA2D_Init 0 */

/* USER CODE END DMA2D_Init 0 */

/* USER CODE BEGIN DMA2D_Init 1 */

/* USER CODE END DMA2D_Init 1 */

hdma2d.Instance = DMA2D;

hdma2d.Init.Mode = DMA2D_M2M;

hdma2d.Init.ColorMode = DMA2D_OUTPUT_RGB565;

hdma2d.Init.OutputOffset = 0;

hdma2d.LayerCfg[1].InputOffset = 0;

hdma2d.LayerCfg[1].InputColorMode = DMA2D_INPUT_RGB565;

hdma2d.LayerCfg[1].AlphaMode = DMA2D_NO_MODIF_ALPHA;

hdma2d.LayerCfg[1].InputAlpha = 0;

hdma2d.LayerCfg[1].AlphaInverted = DMA2D_REGULAR_ALPHA;

hdma2d.LayerCfg[1].RedBlueSwap = DMA2D_RB_REGULAR;

hdma2d.LayerCfg[1].ChromaSubSampling = DMA2D_NO_CSS;

if (HAL_DMA2D_Init(&hdma2d) != HAL_OK)

{

Error_Handler();

}

if (HAL_DMA2D_ConfigLayer(&hdma2d, 1) != HAL_OK)

{

Error_Handler();

}

/* USER CODE BEGIN DMA2D_Init 2 */

/* USER CODE END DMA2D_Init 2 */

}

/**

* @brief LTDC Initialization Function

* @param None

* @retval None

*/

static void MX_LTDC_Init(void)

{

/* USER CODE BEGIN LTDC_Init 0 */

/* USER CODE END LTDC_Init 0 */

LTDC_LayerCfgTypeDef pLayerCfg = {0};

/* USER CODE BEGIN LTDC_Init 1 */

/* USER CODE END LTDC_Init 1 */

hltdc.Instance = LTDC;

hltdc.Init.HSPolarity = LTDC_HSPOLARITY_AL;

hltdc.Init.VSPolarity = LTDC_VSPOLARITY_AL;

hltdc.Init.DEPolarity = LTDC_DEPOLARITY_AL;

hltdc.Init.PCPolarity = LTDC_PCPOLARITY_IPC;

hltdc.Init.HorizontalSync = 39;

hltdc.Init.VerticalSync = 9;

hltdc.Init.AccumulatedHBP = 85;

hltdc.Init.AccumulatedVBP = 32;

hltdc.Init.AccumulatedActiveW = 885;

hltdc.Init.AccumulatedActiveH = 512;

hltdc.Init.TotalWidth = 1095;

hltdc.Init.TotalHeigh = 534;

hltdc.Init.Backcolor.Blue = 0;

hltdc.Init.Backcolor.Green = 0;

hltdc.Init.Backcolor.Red = 0;

if (HAL_LTDC_Init(&hltdc) != HAL_OK)

{

Error_Handler();

}

pLayerCfg.WindowX0 = 0;

pLayerCfg.WindowX1 = 800;

pLayerCfg.WindowY0 = 0;

pLayerCfg.WindowY1 = 480;

pLayerCfg.PixelFormat = LTDC_PIXEL_FORMAT_RGB565;

pLayerCfg.Alpha = 255;

pLayerCfg.Alpha0 = 0;

pLayerCfg.BlendingFactor1 = LTDC_BLENDING_FACTOR1_CA;

pLayerCfg.BlendingFactor2 = LTDC_BLENDING_FACTOR2_CA;

pLayerCfg.FBStartAdress = 0;

pLayerCfg.ImageWidth = 800;

pLayerCfg.ImageHeight = 480;

pLayerCfg.Backcolor.Blue = 0;

pLayerCfg.Backcolor.Green = 0;

pLayerCfg.Backcolor.Red = 0;

if (HAL_LTDC_ConfigLayer(&hltdc, &pLayerCfg, 0) != HAL_OK)

{

Error_Handler();

}

/* USER CODE BEGIN LTDC_Init 2 */

/* USER CODE END LTDC_Init 2 */

}

/**

* @brief TIM2 Initialization Function

* @param None

* @retval None

*/

static void MX_TIM2_Init(void)

{

/* USER CODE BEGIN TIM2_Init 0 */

/* USER CODE END TIM2_Init 0 */

TIM_ClockConfigTypeDef sClockSourceConfig = {0};

TIM_MasterConfigTypeDef sMasterConfig = {0};

/* USER CODE BEGIN TIM2_Init 1 */

/* USER CODE END TIM2_Init 1 */

htim2.Instance = TIM2;

htim2.Init.Prescaler = 23999;

htim2.Init.CounterMode = TIM_COUNTERMODE_UP;

htim2.Init.Period = 9;

htim2.Init.ClockDivision = TIM_CLOCKDIVISION_DIV1;

htim2.Init.AutoReloadPreload = TIM_AUTORELOAD_PRELOAD_DISABLE;

if (HAL_TIM_Base_Init(&htim2) != HAL_OK)

{

Error_Handler();

}

sClockSourceConfig.ClockSource = TIM_CLOCKSOURCE_INTERNAL;

if (HAL_TIM_ConfigClockSource(&htim2, &sClockSourceConfig) != HAL_OK)

{

Error_Handler();

}

sMasterConfig.MasterOutputTrigger = TIM_TRGO_RESET;

sMasterConfig.MasterSlaveMode = TIM_MASTERSLAVEMODE_DISABLE;

if (HAL_TIMEx_MasterConfigSynchronization(&htim2, &sMasterConfig) != HAL_OK)

{

Error_Handler();

}

/* USER CODE BEGIN TIM2_Init 2 */

/* USER CODE END TIM2_Init 2 */

}

/* FMC initialization function */

static void MX_FMC_Init(void)

{

/* USER CODE BEGIN FMC_Init 0 */

/* USER CODE END FMC_Init 0 */

FMC_SDRAM_TimingTypeDef SdramTiming = {0};

/* USER CODE BEGIN FMC_Init 1 */

/* USER CODE END FMC_Init 1 */

/** Perform the SDRAM1 memory initialization sequence

*/

hsdram1.Instance = FMC_SDRAM_DEVICE;

/* hsdram1.Init */

hsdram1.Init.SDBank = FMC_SDRAM_BANK2;

hsdram1.Init.ColumnBitsNumber = FMC_SDRAM_COLUMN_BITS_NUM_8;

hsdram1.Init.RowBitsNumber = FMC_SDRAM_ROW_BITS_NUM_12;

hsdram1.Init.MemoryDataWidth = FMC_SDRAM_MEM_BUS_WIDTH_16;

hsdram1.Init.InternalBankNumber = FMC_SDRAM_INTERN_BANKS_NUM_4;

hsdram1.Init.CASLatency = FMC_SDRAM_CAS_LATENCY_2;

hsdram1.Init.WriteProtection = FMC_SDRAM_WRITE_PROTECTION_DISABLE;

hsdram1.Init.SDClockPeriod = FMC_SDRAM_CLOCK_PERIOD_2;

hsdram1.Init.ReadBurst = FMC_SDRAM_RBURST_ENABLE;

hsdram1.Init.ReadPipeDelay = FMC_SDRAM_RPIPE_DELAY_0;

/* SdramTiming */

SdramTiming.LoadToActiveDelay = 2;

SdramTiming.ExitSelfRefreshDelay = 7;

SdramTiming.SelfRefreshTime = 4;

SdramTiming.RowCycleDelay = 7;

SdramTiming.WriteRecoveryTime = 3;

SdramTiming.RPDelay = 2;

SdramTiming.RCDDelay = 2;

if (HAL_SDRAM_Init(&hsdram1, &SdramTiming) != HAL_OK)

{

Error_Handler( );

}

/* USER CODE BEGIN FMC_Init 2 */

__IO uint32_t tmpmrd = 0;

/* Step 1: Configure a clock configuration enable command */

Command.CommandMode = FMC_SDRAM_CMD_CLK_ENABLE;

Command.CommandTarget = FMC_SDRAM_CMD_TARGET_BANK2;

Command.AutoRefreshNumber = 1;

Command.ModeRegisterDefinition = 0;

/* Send the command */

HAL_SDRAM_SendCommand(&hsdram1, &Command, SDRAM_TIMEOUT);

/* Step 2: Insert 100 us minimum delay */

/* Inserted delay is equal to 1 ms due to systick time base unit (ms) */

HAL_Delay(1);

/* Step 3: Configure a PALL (precharge all) command */

Command.CommandMode = FMC_SDRAM_CMD_PALL;

Command.CommandTarget = FMC_SDRAM_CMD_TARGET_BANK2;

Command.AutoRefreshNumber = 1;

Command.ModeRegisterDefinition = 0;

/* Send the command */

HAL_SDRAM_SendCommand(&hsdram1, &Command, SDRAM_TIMEOUT);

/* Step 4: Configure an Auto Refresh command */

Command.CommandMode = FMC_SDRAM_CMD_AUTOREFRESH_MODE;

Command.CommandTarget = FMC_SDRAM_CMD_TARGET_BANK2;

Command.AutoRefreshNumber = 8;

Command.ModeRegisterDefinition = 0;

/* Send the command */

HAL_SDRAM_SendCommand(&hsdram1, &Command, SDRAM_TIMEOUT);

/* Step 5: Program the external memory mode register */

tmpmrd = (uint32_t)SDRAM_MODEREG_BURST_LENGTH_1 |\

SDRAM_MODEREG_BURST_TYPE_SEQUENTIAL |\

SDRAM_MODEREG_CAS_LATENCY_2 |\

SDRAM_MODEREG_OPERATING_MODE_STANDARD |\

SDRAM_MODEREG_WRITEBURST_MODE_SINGLE;

Command.CommandMode = FMC_SDRAM_CMD_LOAD_MODE;

Command.CommandTarget = FMC_SDRAM_CMD_TARGET_BANK2;

Command.AutoRefreshNumber = 1;

Command.ModeRegisterDefinition = tmpmrd;

/* Send the command */

HAL_SDRAM_SendCommand(&hsdram1, &Command, SDRAM_TIMEOUT);

/* Step 6: Set the refresh rate counter */

/* Set the device refresh rate */

HAL_SDRAM_ProgramRefreshRate(&hsdram1, REFRESH_COUNT);

/* USER CODE END FMC_Init 2 */

}

/**

* @brief GPIO Initialization Function

* @param None

* @retval None

*/

static void MX_GPIO_Init(void)

{

GPIO_InitTypeDef GPIO_InitStruct = {0};

/* USER CODE BEGIN MX_GPIO_Init_1 */

/* USER CODE END MX_GPIO_Init_1 */

/* GPIO Ports Clock Enable */

__HAL_RCC_GPIOI_CLK_ENABLE();

__HAL_RCC_GPIOF_CLK_ENABLE();

__HAL_RCC_GPIOH_CLK_ENABLE();

__HAL_RCC_GPIOC_CLK_ENABLE();

__HAL_RCC_GPIOA_CLK_ENABLE();

__HAL_RCC_GPIOB_CLK_ENABLE();

__HAL_RCC_GPIOG_CLK_ENABLE();

__HAL_RCC_GPIOE_CLK_ENABLE();

__HAL_RCC_GPIOD_CLK_ENABLE();

/*Configure GPIO pin : PA0 */

GPIO_InitStruct.Pin = GPIO_PIN_0;

GPIO_InitStruct.Mode = GPIO_MODE_INPUT;

GPIO_InitStruct.Pull = GPIO_PULLDOWN;

HAL_GPIO_Init(GPIOA, &GPIO_InitStruct);

/* USER CODE BEGIN MX_GPIO_Init_2 */

/* USER CODE END MX_GPIO_Init_2 */

}

/* USER CODE BEGIN 4 */

/* USER CODE END 4 */

/* MPU Configuration */

void MPU_Config(void)

{

MPU_Region_InitTypeDef MPU_InitStruct = {0};

/* Disables the MPU */

HAL_MPU_Disable();

/** Initializes and configures the Region and the memory to be protected

*/

MPU_InitStruct.Enable = MPU_REGION_ENABLE;

MPU_InitStruct.Number = MPU_REGION_NUMBER0;

MPU_InitStruct.BaseAddress = 0xD0000000;

MPU_InitStruct.Size = MPU_REGION_SIZE_8MB;

MPU_InitStruct.SubRegionDisable = 0x0;

MPU_InitStruct.TypeExtField = MPU_TEX_LEVEL0;

MPU_InitStruct.AccessPermission = MPU_REGION_FULL_ACCESS;

MPU_InitStruct.DisableExec = MPU_INSTRUCTION_ACCESS_ENABLE;

MPU_InitStruct.IsShareable = MPU_ACCESS_NOT_SHAREABLE;

MPU_InitStruct.IsCacheable = MPU_ACCESS_CACHEABLE;

MPU_InitStruct.IsBufferable = MPU_ACCESS_NOT_BUFFERABLE;

HAL_MPU_ConfigRegion(&MPU_InitStruct);

/* Enables the MPU */

HAL_MPU_Enable(MPU_PRIVILEGED_DEFAULT);

}

/**

* @brief Period elapsed callback in non blocking mode

* @note This function is called when TIM1 interrupt took place, inside

* HAL_TIM_IRQHandler(). It makes a direct call to HAL_IncTick() to increment

* a global variable "uwTick" used as application time base.

* @param htim : TIM handle

* @retval None

*/

void HAL_TIM_PeriodElapsedCallback(TIM_HandleTypeDef *htim)

{

/* USER CODE BEGIN Callback 0 */

lv_tick_inc(1);

/* USER CODE END Callback 0 */

if (htim->Instance == TIM1) {

HAL_IncTick();

}

/* USER CODE BEGIN Callback 1 */

/* USER CODE END Callback 1 */

}

/**

* @brief This function is executed in case of error occurrence.

* @retval None

*/

void Error_Handler(void)

{

/* USER CODE BEGIN Error_Handler_Debug */

/* User can add his own implementation to report the HAL error return state */

__disable_irq();

while (1)

{

}

/* USER CODE END Error_Handler_Debug */

}

#ifdef USE_FULL_ASSERT

/**

* @brief Reports the name of the source file and the source line number

* where the assert_param error has occurred.

* @param file: pointer to the source file name

* @param line: assert_param error line source number

* @retval None

*/

void assert_failed(uint8_t *file, uint32_t line)

{

/* USER CODE BEGIN 6 */

/* User can add his own implementation to report the file name and line number,

ex: printf("Wrong parameters value: file %s on line %d\r\n", file, line) */

/* USER CODE END 6 */

}

#endif /* USE_FULL_ASSERT */